The datasheet for the the Spartan 6 FPGA devices is available below:

https://www.xilinx.com/support/documentation/data_sheets/ds162.pdf

Rather than write a lot of VHDL code to generate the clocks we need we are going to use a feature of Xilinx WebISE 14.7 to write the code for us - cool huh.

Lets set some parameters! Lets generate a 200 MHz clock and send it to one of the output pins and then view this on an oscilloscope or logic probe. If people are interested the instruction manual for the DCM clock generator is here:

DCM Clock Generator Manual

Lets fire up Xilinx WebISE and start a new project:

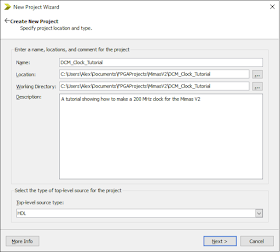

Choose to save the project in a suitable location on your hard disk and give the project a suitable name - I called mine DCM_Clock_Tutorial but any sensible name will do:

Click Next when ready.

Make sure all the settings are the same as in the image below - these are the settings required for the FPGA device on the Mimas V2:

Click Next when ready to display the project summary page:

And finally click Finish to return to the main project screen:

Now right click on the design hierachy window and select add source:

Select VHDL module and give the file a suitable name, I called mine DCM_Clock_Top_Module but another name could be used. It should be something sensible however:

Click Next to continue and add the inputs and outputs. I have chosen to add a signal called CLK as an input and a signal called CLKOUT_200M as an output. If we wanted to we could leave this screen blank and write our own code later.

Click Next to continue and display the summary screen:

Click finish to return to the main project window and see the automatically generated code:

I prefer to delete most of the comments as they don't add any value at this point however...they can be left or completed if required.

At this point it is always a good idea to save things.

We will return to write VHDL code here later but for now lets add another new source, this time select IP (Core Generator and Architecture Wizard) and give the file a suitable name:

Click Next when ready and then wait for WebISE to load up all of the available IP cores for the Spartan 6 family:

Type Clock into the search field:

Click Next when ready:

Click Finish and wait for WebISE to build the code and load the wizard.

Make sure the settings are as shown below:

The options selected are for the Mimas V2 which has a 100 MHz source clock. We have also chosen to reduce jitter which should make the clock more accurate and we have decided to let WebISE select the most applicable mode for us - Click Next when ready to continue:

Ensure the same settings have been selected and click Next when ready.

Ensure the settings are the same as above and click Next when ready - for this tutorial we don't need a reset input or locked input.

These are the IO functions which will be automatically created by the wizard when the code is generated. Click Next when ready.

These are the names that will be used for the input clock signals and output clock signals - Click Next when ready.

Click Generate when ready and wait until the code has been generated.

Now here is where we could do things in multiple ways. We could add code to the VHDL module or we can take advantage of WebISE and have it write the code for us...I'm going to take the easy option. Click on the newly created ClockMultiplier200M module in the Hierachy Window and then expand the CORE Generator process icon and select View HDL Instantiation Template:

Open the file and scroll down to line 67:

Select and copy the VHDL code from line 67 to line 76:

Paste this code into the VHDL top module code at line 11 in the header of the architecture function:

Now return to the HDL Instantiation Template and select the code on line 82 to line 89 and copy it. Then paste that code into the top module code on line 22 between the begin and end Behavioural lines:

Go to line 22 and change the text 'your_instance_name to something sensible, I typed clockMultiplier:

Next we need to generate the implementation constraints file. Right click on the hierarchy window and select Add new source like before:

Click Next when ready.

Click Finish when ready.

We need to create the implementation constraints code specifically for the Mimas V2. I tend to use the original supplied by Numato Labs and then modify it to suit our purposes. Copy and paste the code below into the text editor in WebISE:

#******************************************************************#

# UCF for Mimas V2 # # #

#******************************************************************#

CONFIG VCCAUX = "3.3" ;

NET "CLK" LOC = V10 | IOSTANDARD = LVCMOS33 | PERIOD = 100MHz ;

NET "CLKOUT_200M" LOC = T10 | IOSTANDARD = LVCMOS33 | DRIVE = 8 | SLEW = FAST | OUT_TERM = UNTUNED_50 ; #Pin 4

I chose to set the impedance to 50 ohms so that it can be properly measured with an oscilloscope.

Lets save our work and upload it to the FPGA - Click on the implement top module arrow button and then after those processes are complete create a bitfile. Navigate the to folder where the project was stored and locate the newly created bitfile! Then load up the MimasV2 Configuration tool and connect up your Mimas to your PC. Select the appropriate COM port and then....

Then upload it to the Mimas V2 development board:

Once uploaded Pin 4 of the output Bank P8 should have a clock signal on it which can be viewed with an oscilloscope or logic probe. In truth these clock signals are designed to be used internally within your FPGA design and not brought out to a pin. The signal won't be particularly square or have a a fast rising edge.

Here is a photo I took of a signal from the FPGA measured with an oscilloscope - it looks more like a sine wave!

That's all for now - Langster

Here is a photo I took of a signal from the FPGA measured with an oscilloscope - it looks more like a sine wave!

That's all for now - Langster

Thanks for your blog post.

ReplyDeleteCan you show how to generate frequency greater than 400 MHz by using bufplls in design